Error message控制

前面讲到,PCIe错误消息(Error Message)是需要上报给PCIe域的老大Root Complex的。今天详细的来看看是如何支持错误信息上报控制的。

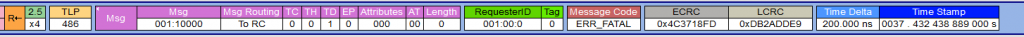

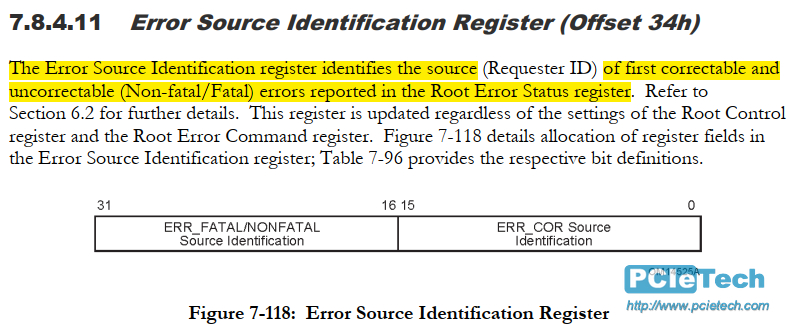

如果Root Port支持AER(Advanced Error Report),RC从message中提取RequesterID字段,并记录的Root port的Error Source Identification寄存器中,这个BDF号就是出错的设备。不过很多时候这个BDF是捕获不到的,或者出现多个错误,RC只能提取第一个错误的RequesterID。因此,需要driver遍历Root Port下的所有设备,检查哪些设备出现了错误。

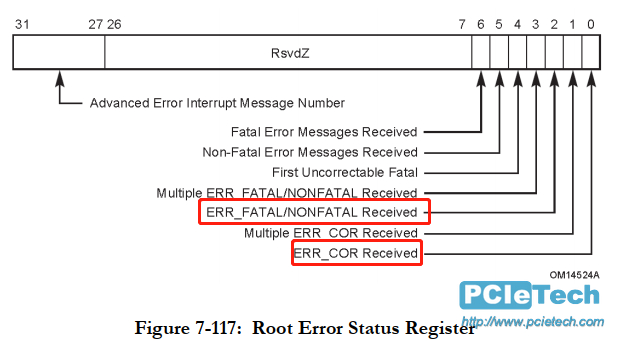

如果Root Port支持AER,则收到errormessage(根据error code可以分为ERR_COR/ERR_NONFATAL/ERR_FATAL)或者Root port自己检查到对应错误时,会记录到Root Port的Root Error Status寄存器。

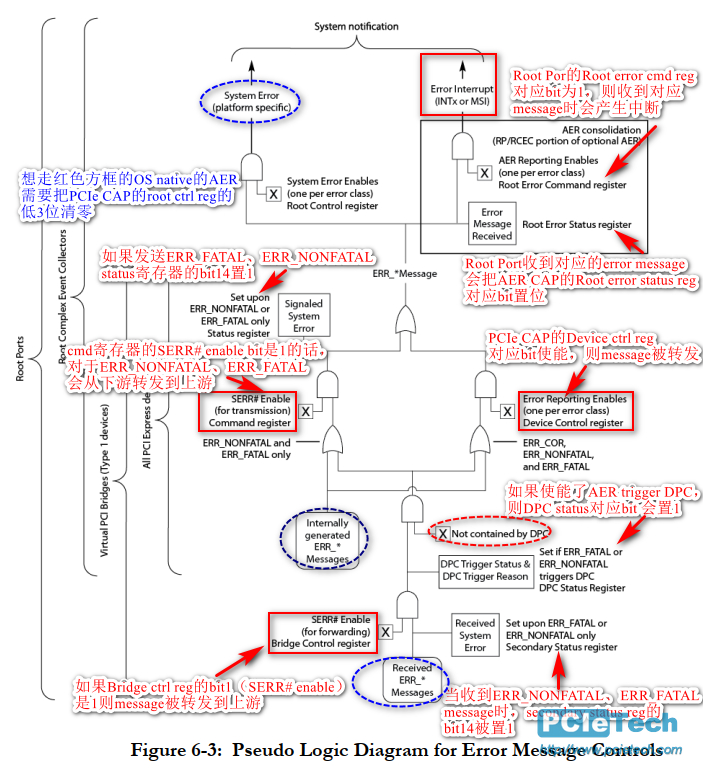

Error message从PCIe设备产生到路由到对应Root Por涉及一系列的控制寄存器和状态寄存器。

Root Port下面的设备或Root Port本身发生PCIe错误想产生MSI中断话,需要关注哪些寄存器呢?

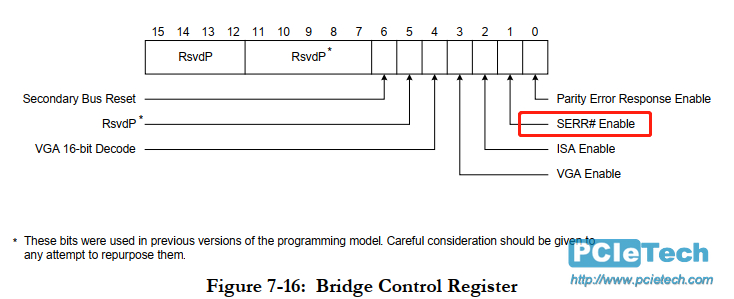

A.整条链路上所有bridge的Bridge ctrl reg的SERR# bit

如果该bit没有使能,则bridge不会往上游转发下游的设备上报的error message。如果是Root port本身产生的错误的则不需要关注该bit。

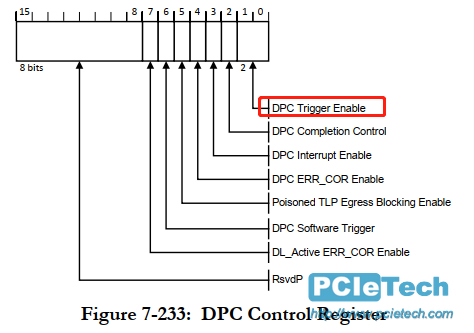

B.整条链路上支持DPC的设备(DP和RP)是否使能了DPC

如果使能了DPC trigger enable,下游设备发送的ERR_FATAL或ERR_NONFATAL的error message会被DPC拦截。

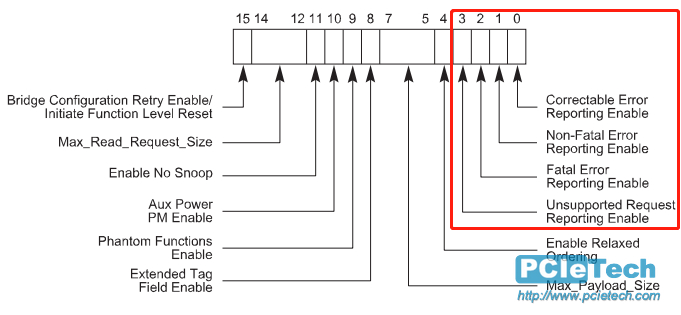

C.整条链路上的所有PCIe设备的Device ctrl reg的对应bit是否使能

Device ctrl reg的低4bit是一个比较大的控制开关,分布控制ERR_COR message、ERR_NONFATAL message、ERR_FATAL message和Unsupported

Request的发送。

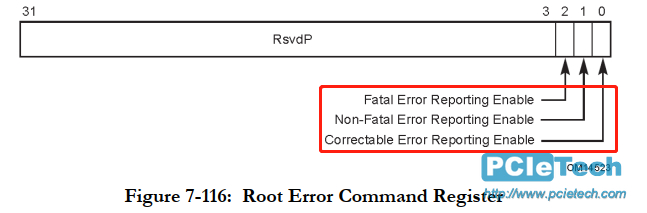

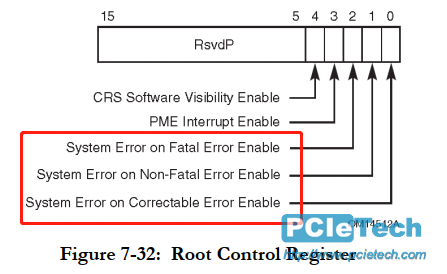

D.Root port的Root error command reg对应bit是否为1

如果Root error commandreg对应bit为1,则Root port本身或者Root port收到下游设备上报错误时才会产生中断。

E. Root Port的Root ctrl reg对应bit是否清零

如果Root ctrl reg对应bit没有清零,则会走左边的分支产生system error,对X86而言这是一条带外的pin。

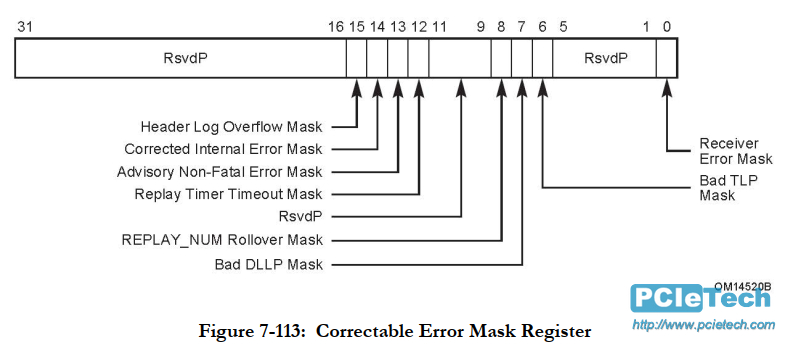

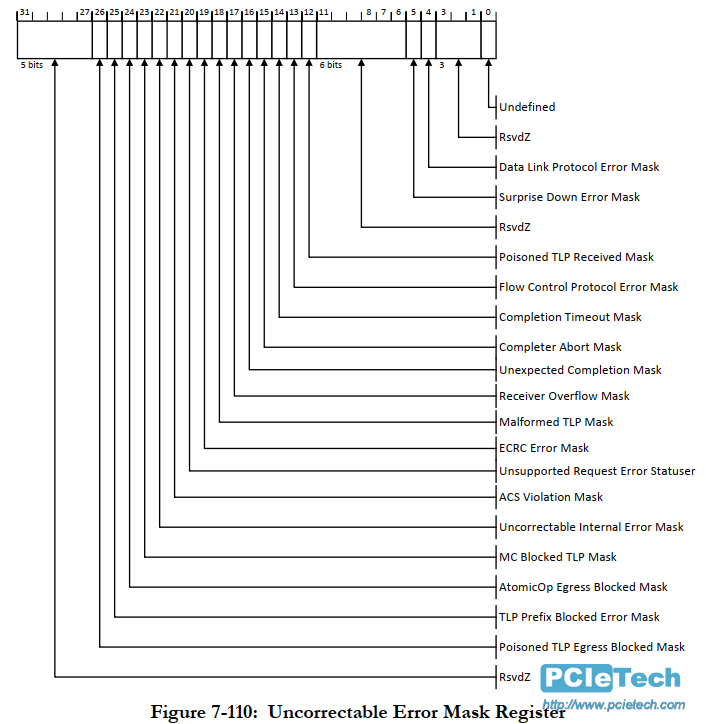

F. 整个链路上的PCIe设备error mask reg是否置1

如果error mask reg为1,则产生对应错误时,只会更新PCIe CAP的error status寄存器,不会产生error message。

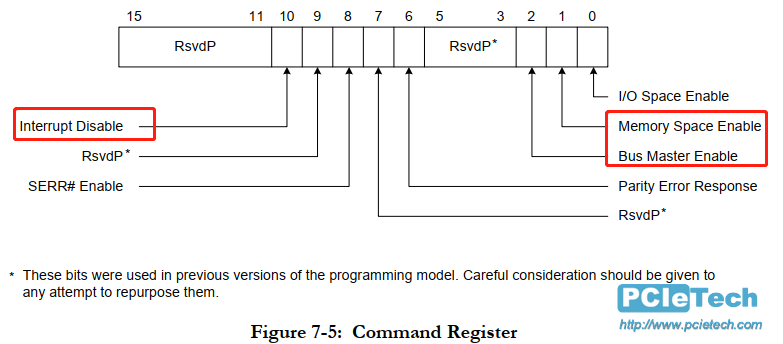

G.Command寄存器的memory space enable bit和bus master enable bit是否为1,interrupt disable是否为1

MSI中断本质上是一个memory write请求,Command寄存器的memory space enable bit和bus master enable bit负责MSI中断的产生和转发。

Interrupt disable是禁止INTx中断。由于,INTx优先级比MSI中断要高,该bit需要禁止。

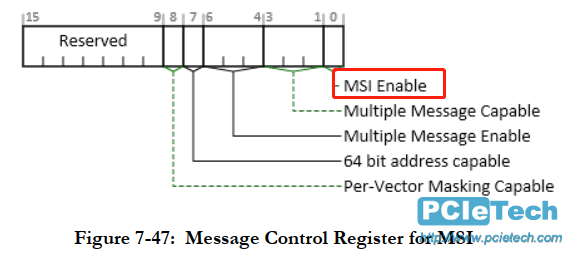

H.Root Port的MSI enable是否为1

Error message会路由到Root Port,如果想产生MSI中断,root port的MSI enable bit需要为1。

I. 一些特殊的reg

由于每款芯片实现不一样,有些芯片还有一些特殊的reg控制使用MSI中断或者其他的中断。根据具体芯片设置,这里就不讨论了。