关于Link的更多理解

Link的速率在初始化以后确定,所有lane的信号速率一样。如PCIe 3.0情况下,每条lane每秒每个方向都提供8G的带宽。假设是X4的Link,则链路每个方向的带宽为32GT/s(8.0X4)。

Link的初始化和协商,确定lane宽度以及速率,是不需要操作系统或者软件参与的,纯粹是芯片的硬件行为。

协议定义的允许的宽度组合为x1, x2, x4, x8, x12, x16, 以及x32 Lane。每条Link至少有一个lane。例如,常见的SSD的上的M.2和U.2(SFF-8639)提供了x2的PCIe link。(注:新的协议已经有支持x4)。x32的link由于物理尺寸太过庞大,一般情况下并不使用。

PCIe链路是没有边带信号的,当然也没有单独的时钟线。PCIe的时钟是编码嵌入在link里的。接收端依靠同样的逻辑解析出时钟和数据。

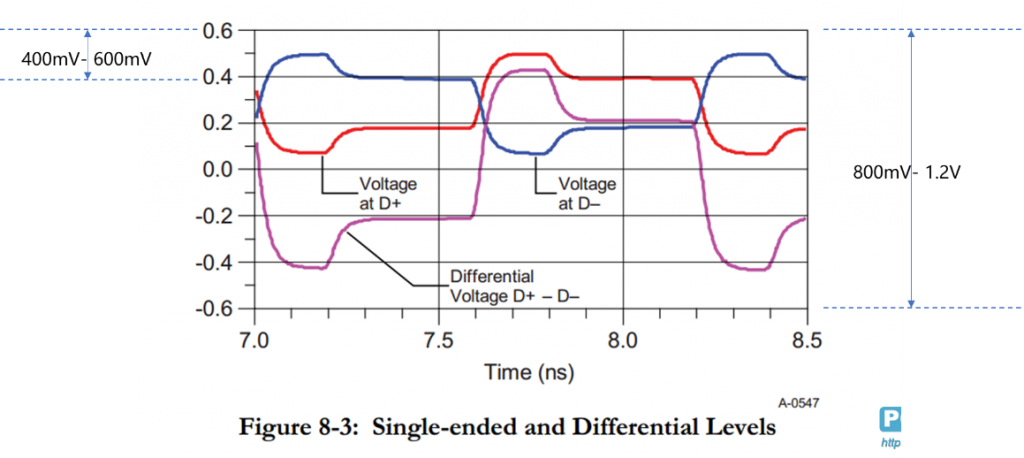

对于每一条lane上的差分信号,差分信号的电压(D+减D-)大约在800mV~1.2V之间。对于D+或者D-的单端电压大约在400-600mV之间。

思考:

![]() 数据在不同的lane上,是怎么分配传输的?

数据在不同的lane上,是怎么分配传输的?

上期问答:

![]() 可以任意条lane组成一个link么?

可以任意条lane组成一个link么?

不可以。协议规定了只能是x1, x2, x4, x8, x12, x16, x32。

![]() lane0和lane1可以交换顺序交叉连接么?

lane0和lane1可以交换顺序交叉连接么?

可以。协议上这种特性叫Lane Reversal。不过需要注意的是,这个是可选特性,不是每个设备都支持的。

请问如果理解PCIE 中port的概念? port, link, function之前有什么关系?

Port是switch/RC相关的概念,link是port、port之间,或者port、device之间的链路。function是device的一个功能。

那么channel 是什么呢? 是1 lane=4 channel吗?

严格讲,lane跟channel没有啥关系。pcie里面的channel是指virtual channel,QoS相关的内容。并非物理上的通道。